## A Design Flow for the Development, Characterization, and Refinement of System Level Architectural Services

by

Douglas Michael Densmore

B.S. (University of Michigan, Ann Arbor) 2001 M.S. (University of California, Berkeley) 2004

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Alberto Sangiovanni-Vincentelli, Chair

Professor Jan Rabaey

Professor Lee Schruben

Spring 2007

UMI Number: 3275390

#### **INFORMATION TO USERS**

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform 3275390

Copyright 2007 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# A Design Flow for the Development, Characterization, and Refinement of System Level Architectural Services

Copyright 2007 by Douglas Michael Densmore

#### **Abstract**

A Design Flow for the Development, Characterization, and Refinement of System Level

Architectural Services

by

Douglas Michael Densmore

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Alberto Sangiovanni-Vincentelli, Chair

The electronics industry is facing serious challenges because of the increased demand on functionality and strong pressures on both time-to-market and cost requirements. The complexity designers have to deal with creates design quality problems that force serious delays in product introductions and even product recalls. There is a need for methodologies and tools that can drastically reduce design errors and costs. Electronic System Level (ESL) tools attempt to fulfill this need by increasing the abstraction and modularity by which designs can be specified. However, simply because these design styles are introduced, this does not automatically imply an acceptable level of accuracy and efficiency required for widespread adoption and eventual success. This thesis introduces a design flow which improves abstraction and modularity while remaining highly accurate and efficient. Specifically this work explores a Platform-Based Design approach to model architectural services.

Platform-Based Design is a methodology in which purely functional descriptions of a system are top-down assigned (or mapped) to architecture services which have their models for capabilities and costs exported from the bottom up. Architecture services are a set of library elements characterized by their capabilities (what functionality they support) and costs (execution time, power, etc). These libraries of components "parametrize" the set of architecture services that can be chosen by the designer to implement functionality and limit the design space thus favoring design re-use. The design process then proceeds toward implementation by binding functionality to architectures composed of elements from the library. The components that form a platform instance are selected by evaluating their capability of supporting the mapped functionality within the design constraints and by optimizing objective functions. The design space exploration can be done via simulation of the mapped designs by changing the mapping and the choice of

2

components. Keeping the architecture services and the functional aspects of the design separate facilitates design space exploration since this exploration requires only the change of the mapping of functions to architectural services or the selection of a different set of components to build the platform instance. In either case, only a minor change to the description of the design is required to perform the evaluation.

The design flow proposed in this thesis specifically focuses on how to create architecture service models of programmable platforms (FPGAs for example). These architecture service models are created at the transaction level, are preemptable, and export their abilities to the mapping process. An architecture service library is described for Xilinx's Virtex II Pro FPGA. If this library is used, a method exists to extract the architecture topology to program an FPGA device directly, thus avoiding error prone manual techniques. As a consequence of this programmable platform modeling style, the models can be annotated directly with characterization data from a concurrent characterization process to be described.

Finally, in order to support various levels of abstraction in these architecture service models, a refinement verification flow will be discussed as well. Three styles will be proposed each with their own emphasis (event based, interface based, compositional component based). They are each deployed depending on the designer's needs and the environment in which the architecture is developed. These needs include changing the topology of the architecture model, modifying the operation of the architecture service, and the exploring the tradeoffs between how one expresses the services themselves and the simulation infrastructure which schedules the use of those services.

To provide a proof of concept of these techniques, several design scenarios are explored. These scenarios include Motion-JPEG encoding, an H.264 deblocking filter, an SPI-5 networking protocol, and a communication structure of a highly concurrent system architecture (FLEET). The results show that not only is the proposed design flow more accurate and modular than other approaches but also that it prevents the selection of more poorly performing designs or the selection of incorrectly functioning designs through its emphasis on the preservation of fidelity.

Professor Alberto Sangiovanni-Vincentelli Dissertation Committee Chair

#### For Mom and Dad

When you comin' home son? I don't know when, but we'll get together then...

#### Para Remolachita

¡Colorín colorado, esta tesis se ha acabado! Besitos

### **Contents**

| Li | st of I | ligures                                        | V    |

|----|---------|------------------------------------------------|------|

| Li | st of T | Tables                                         | viii |

| 1  | Intr    | oduction                                       | 1    |

|    |         | 1.0.1 Chapter Organization                     | 5    |

|    | 1.1     | Motivating Factors                             | 6    |

|    |         | 1.1.1 Heterogeneity                            | 6    |

|    |         | 1.1.2 Complexity                               | 9    |

|    |         | 1.1.3 Time to Market                           | 11   |

|    | 1.2     | 1st Focus: System Level Design                 | 12   |

|    | 1.3     | 2nd Focus: Programmable Architecture Services  | 15   |

|    | 1.4     | Thesis Contribution                            | 20   |

|    |         | 1.4.1 Naïve Design Flow                        | 21   |

|    |         | 1.4.2 Proposed Design Flow                     | 21   |

|    | 1.5     | Thesis Outline                                 | 23   |

| 2  | Syst    | em Level Architecture Services                 | 25   |

|    | •       | 2.0.1 Chapter Organization                     | 27   |

|    | 2.1     | Background and Basic Definitions               | 28   |

|    | 2.2     | Related Work                                   | 31   |

|    | 2.3     | System Level Event Based Architecture Services | 34   |

|    |         | 2.3.1 METROPOLIS Architecture Construction     | 36   |

|    |         | 2.3.2 METRO II Architecture Construction       | 41   |

|    |         | 2.3.3 Architecture Service Extensions          | 44   |

|    | 2.4     | Xilinx Architecture Modeling Exploration       | 48   |

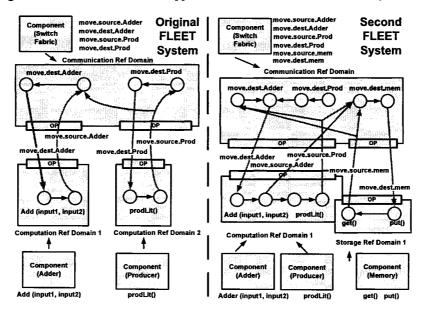

|    | 2.5     | FLEET Architecture Modeling Exploration        | 62   |

|    | 2.6     |                                                | 64   |

|    | 2.7     | ·                                              | 66   |

| 3  | Arc     | hitecture Service Characterization             | 67   |

|    |         | 3.0.1 Chapter Organization                     | 70   |

|    | 3.1     | Platform Characterization                      | 70   |

|    |         |                                                | 71   |

|   | 3.2  | Extraction of Platform Characterization Data                                | 72          |

|---|------|-----------------------------------------------------------------------------|-------------|

|   |      | 3.2.1 Data Extraction Requirements                                          |             |

|   | 3.3  |                                                                             | 75          |

|   | 3.4  | Organization of Platform Characterization Data                              | 78          |

|   |      |                                                                             | 78          |

|   |      |                                                                             | 79          |

|   | 3.5  |                                                                             | 80          |

|   |      |                                                                             | 82          |

|   | 3.6  | Conclusions                                                                 |             |

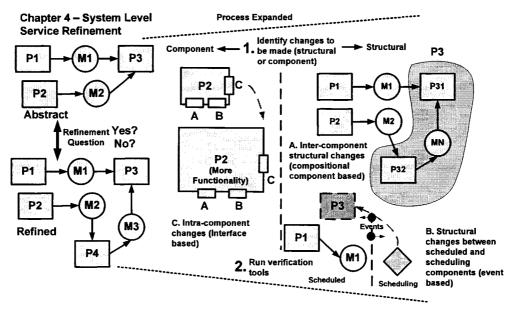

| 4 | Syst | em Level Service Refinement                                                 | 85          |

|   |      | 4.0.1 Chapter Organization                                                  | 87          |

|   | 4.1  | Background and Basic Definitions                                            | 87          |

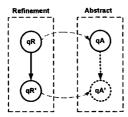

|   |      | 4.1.1 State Equivalence                                                     | 88          |

|   |      | 4.1.2 Trace Containment                                                     | 89          |

|   |      | 4.1.3 Synchronized Parallel Composition                                     | 89          |

|   | 4.2  | Related Work                                                                | 91          |

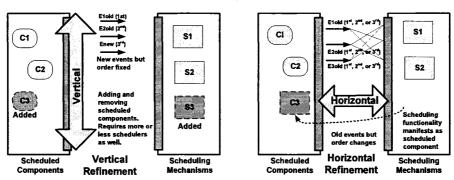

|   | 4.3  | Event Based Service Refinement                                              | 97          |

|   |      | 4.3.1 Proposed Methodology                                                  | 98          |

|   | 4.4  | Interface Based Service Refinement                                          | 13          |

|   |      | 4.4.1 Proposed Methodology                                                  | 14          |

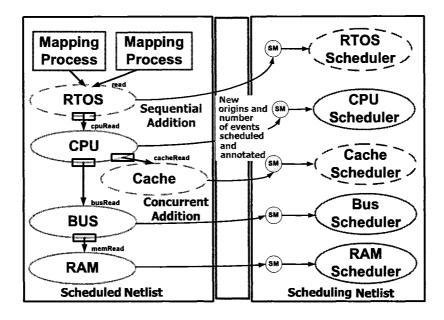

|   | 4.5  | Compositional Component Based Service Refinement                            | 32          |

|   |      | 4.5.1 Proposed Methodology                                                  | 32          |

|   | 4.6  | Conclusions                                                                 | 38          |

| 5 | Desi | · · · · · · · · · · · · · · · · · ·                                         | l <b>40</b> |

|   |      | 5.0.1 Chapter Organization                                                  | 42          |

|   | 5.1  | Characterization Aided Fidelity Example: Motion-JPEG                        | 42          |

|   | 5.2  | Service Aided Mapping Modularity Example: H.264 Deblocking Filter           | 44          |

|   |      | 5.2.1 Application Details                                                   | 46          |

|   |      | 5.2.2 Mapping Details                                                       | 47          |

|   |      | 5.2.3 Design Space Exploration Results                                      | 50          |

|   | 5.3  | Architecture Platform Refinement Example: SPI5 Packet Processing            | 54          |

|   |      | 5.3.1 Application Parameters                                                | 55          |

|   |      | 5.3.2 Architecture Parameters                                               | 55          |

|   |      | 5.3.3 Refinement Based Design Flow                                          | 57          |

|   |      | 5.3.4 Platform Development                                                  |             |

|   |      | 5.3.5 METROPOLIS Models                                                     |             |

|   |      | 5.3.6 Results                                                               |             |

|   | 5.4  | Communication Subsystem Refinement Example: FLEET Communication Structure 1 |             |

|   |      | 5.4.1 Communication Library                                                 |             |

|   |      |                                                                             |             |

| 17 |    |

|----|----|

| 17 | 75 |

|    | -  |

| 17 | 16 |

| 17 | 17 |

| 17 | 18 |

| 17 | 18 |

| 17 | 19 |

| 16 | 'n |

|    |    |

# **List of Figures**

| 1.1  | Overall EDA Revenue Glowth and EDA Design Segment Glowth [Ricos]      |    |

|------|-----------------------------------------------------------------------|----|

| 1.2  | "Methodology Gap" Challenge in EDA                                    | 3  |

| 1.3  | Global Embedded Systems Market [Rav05]                                | 7  |

| 1.4  | Semiconductor Design Cycle Time Decline [Gar05a]                      | 7  |

| 1.5  |                                                                       | 7  |

| 1.6  | Device Component and Communication Heterogeneity [Int06b]             | 8  |

| 1.7  | Growing Gap Between Device Capacity and Designer Productivity [Int99] | 10 |

| 1.8  | Time to Market Revenue Consequences [IBM06]                           | 11 |

| 1.9  | Platform-Based Design Methodology [Alb02]                             | 14 |

| 1.10 | METROPOLIS Design Environment and Organization                        | 15 |

| 1.11 | Makimoto's Wave and Programmable Devices [Tsu00]                      | 17 |

| 1.12 | Naïve Design Flow                                                     | 22 |

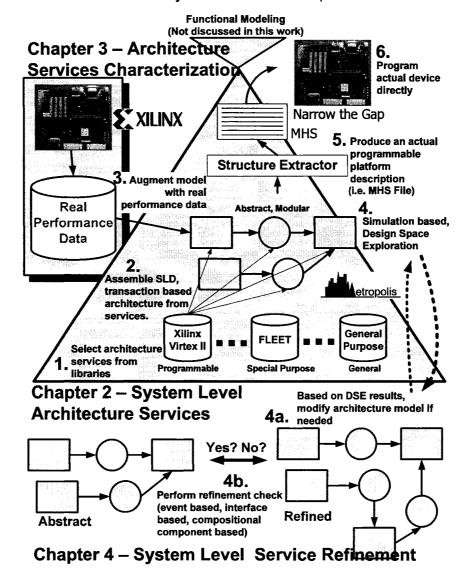

| 1.13 | Proposed Design Flow                                                  | 24 |

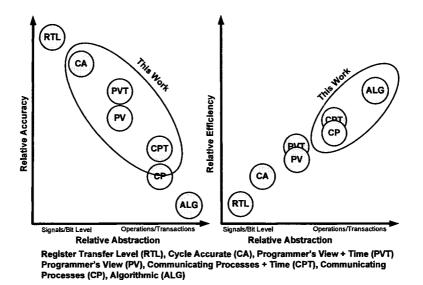

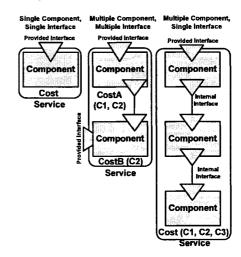

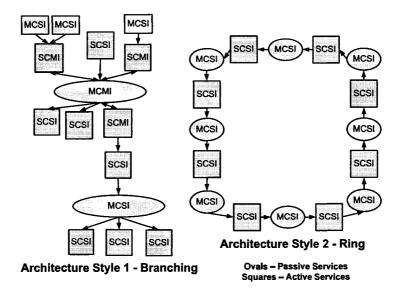

| 2.1  | Proposed Service Style Versus Existing Service Styles                 | 27 |

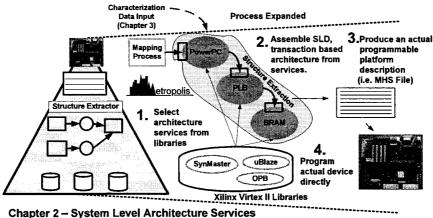

| 2.2  | System Level Architecture Modeling in the Proposed Flow               | 28 |

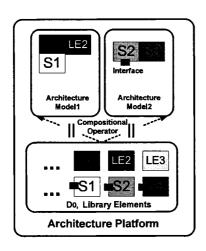

| 2.3  | Architecture Platform Composition and Creation                        | 29 |

| 2.4  | Architecture Service Taxonomy                                         | 29 |

| 2.5  | Composing Architectures Using Services                                | 37 |

| 2.6  | METROPOLIS Process Example Code                                       |    |

| 2.7  | METROPOLIS Medium Example Code                                        |    |

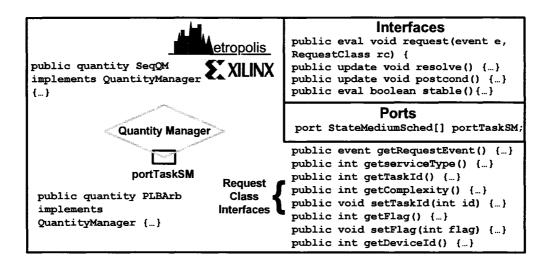

| 2.8  | METROPOLIS Quantity Manager Example Code                              | 39 |

| 2.9  | METROPOLIS State Media Example Code                                   |    |

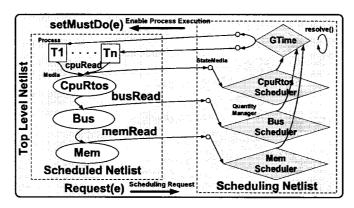

| 2.10 |                                                                       | 40 |

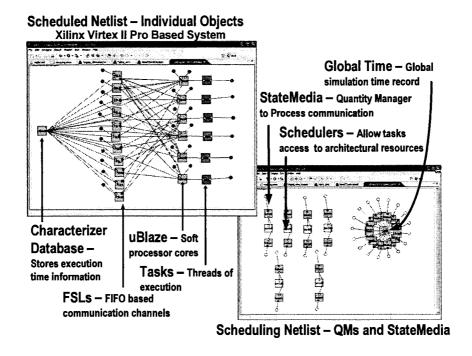

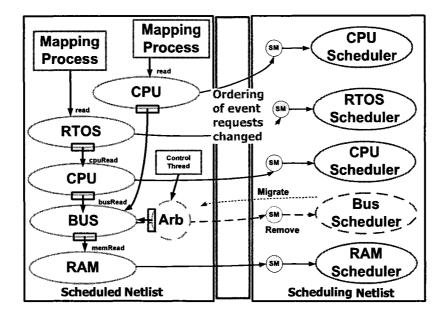

| 2.11 | METROPOLIS Architecture Netlists                                      | 41 |

| 2.12 | Graphical METROPOLIS Architecture Representation                      | 42 |

|      |                                                                       |    |

| 2.14 | Architecture Extensions for Preemption                                | 45 |

| 2.15 | Architecture Extensions for Mapping                                   | 48 |

| 2.16 | METROPOLIS PowerPC Model                                              | 53 |

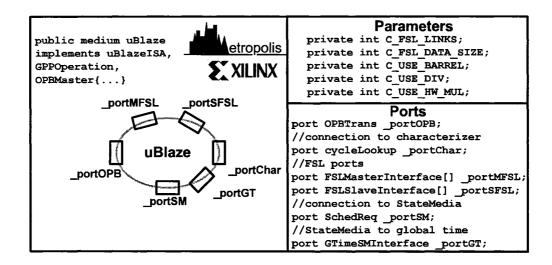

| 2.17 | METROPOLIS MicroBlaze Model                                           | 55 |

| 2.18 | METROPOLIS Synthetic Master/Slave Model                               | 56 |

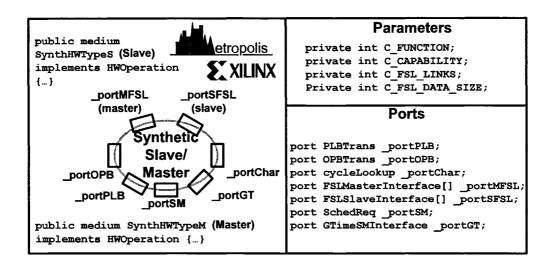

| 2.19 | METROPOLIS PLB Model                                                  | 57 |

|      |                                                                       |    |

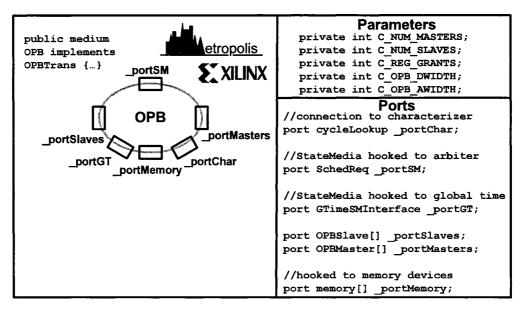

| 2.20 | METROPOLIS OPB Model                                                     |

|------|--------------------------------------------------------------------------|

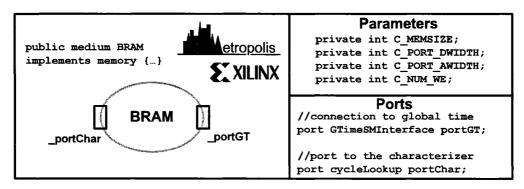

| 2.21 | METROPOLIS BRAM Model                                                    |

| 2.22 | METROPOLIS Quantity Manager Model                                        |

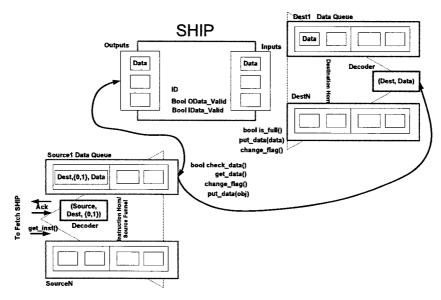

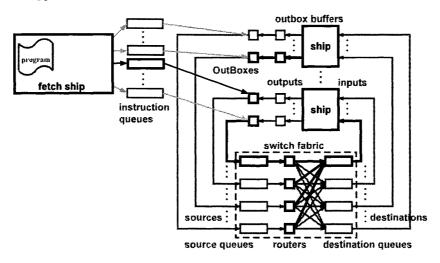

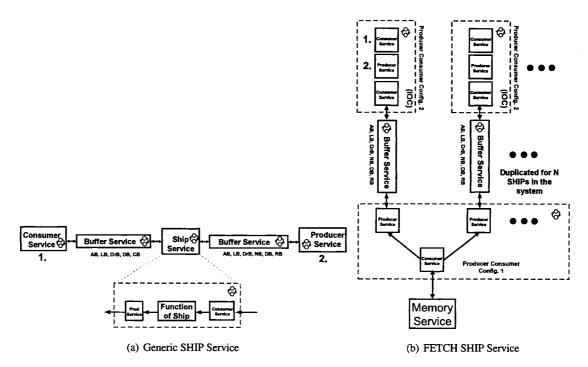

| 2.23 | FLEET SHIP Architecture                                                  |

| 2.24 | FLEET Services Created                                                   |

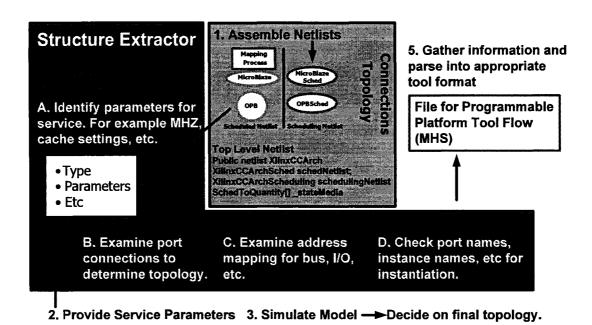

| 2.25 | Automatic Xilinx MHS Extraction                                          |

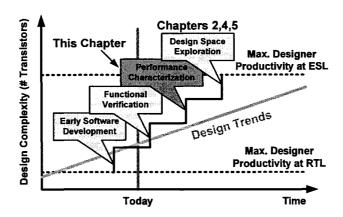

| 3.1  | Transcending RTL Effort with ESL Design Technologies                     |

| 3.2  | Characterization of Architecture Services in the Proposed Design Flow 69 |

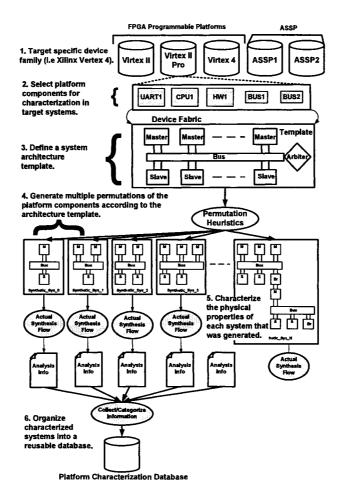

| 3.3  | A Design Flow for Pre-characterizing Programmable Platforms              |

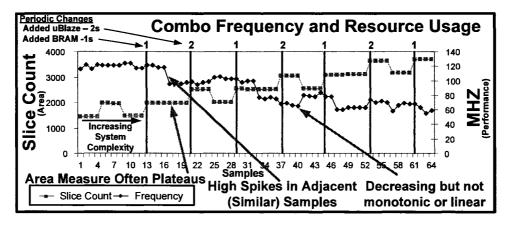

| 3.4  | Combo Systems Resource Usage and Performance                             |

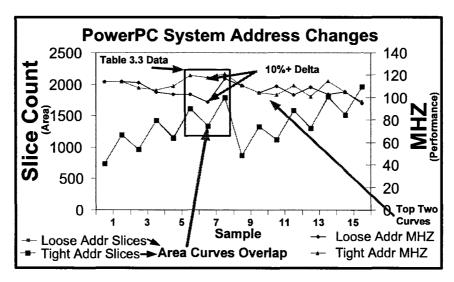

| 3.5  | PowerPC System Performance Analysis                                      |

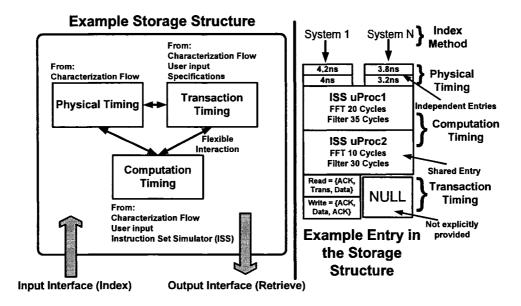

| 3.6  | Characterized Data Organization Proposal                                 |

| 3.7  | METROPOLIS Sample Annotation Semantics Using Characterized Data 83       |

| 4.1  | System Level Service Refinement in the Proposed Design Flow              |

| 4.2  | METROPOLIS Style Refinement Example                                      |

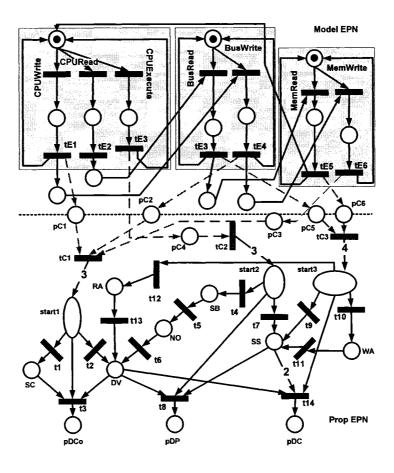

| 4.3  | Event Based Refinement Proposal                                          |

| 4.4  | Vertical Refinement Illustration in METROPOLIS                           |

| 4.5  | Horizontal Refinement Illustration in METROPOLIS                         |

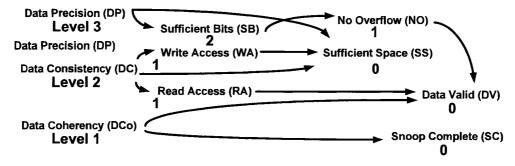

| 4.6  | Macro and MicroProperty Relationships                                    |

| 4.7  | Event Petri Net Example                                                  |

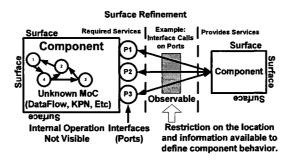

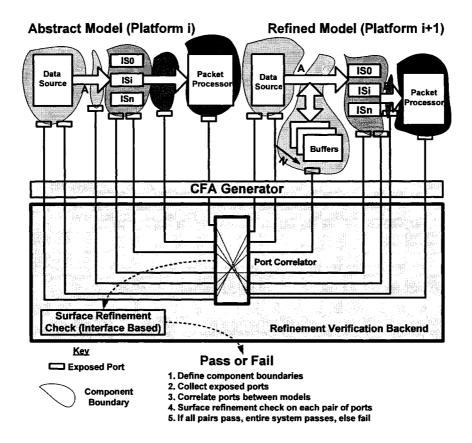

| 4.8  | Interface Based Refinement Proposal                                      |

| 4.9  | Refinement Domains in Interface Based Refinement                         |

| 4.10 | METROPOLIS Code Example                                                  |

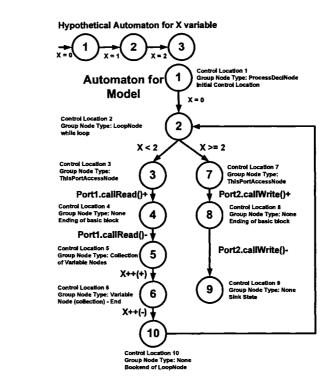

|      | Resulting CFA for Code Example                                           |

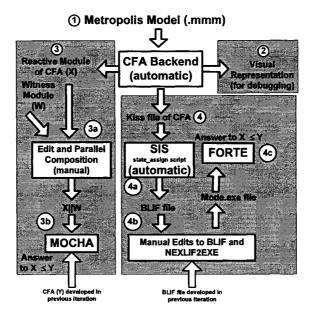

| 4.12 | CFA Visual Representation                                                |

|      | CFA FSM Representation                                                   |

|      | SIS Commands and EXLIF Requirements for FORTE Flow                       |

| 4.15 | Surface Refinement Flows for METROPOLIS                                  |

|      | Strict Transition Refinement                                             |

| 4.17 | Stuttering Transition Refinement                                         |

| 4.18 | Lack of τ-Divergence                                                     |

| 4.19 | External Non-Determinism Preservation                                    |

| 4.20 | .fts for Abstract Consumer LTS                                           |

| 4.21 | .fts for Refined Consumer LTS                                            |

| 4.22 | .inv for Consumer LTSs                                                   |

| 4.23 | .sync for Producer/Consumer LTSs                                         |

| 5.1  | MJPEG Architecture Topologies in METROPOLIS                              |

| 5.2  | Macroblock and Block Border Illustration for H.264 Deblocking Filter     |

| 5.3  | Deblocking Filter Pseudo Code                                            |

| 5.4  | Decomposition of GetStrength Function                                    |

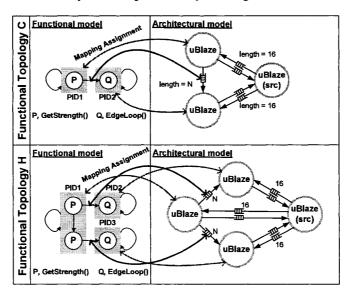

| 5.5  | Decomposition of EdgeLoop Function                                       |

| 56   |                                                                          |

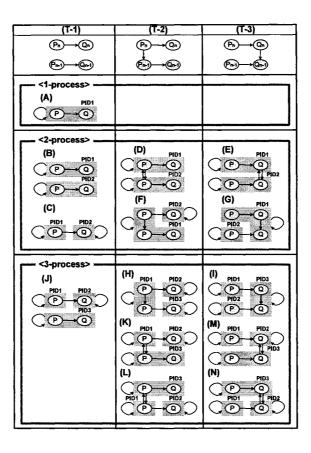

| 5.7  | H.264 Functional Topology Mapping Candidates                         | 150 |

|------|----------------------------------------------------------------------|-----|

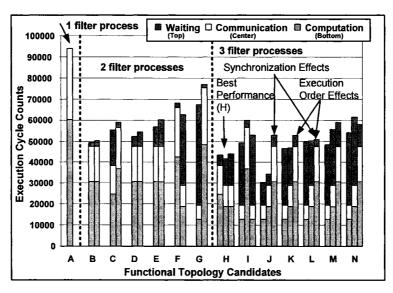

| 5.8  | METROPOLIS H.264 Simulation Results for All Candidate Topologies     | 151 |

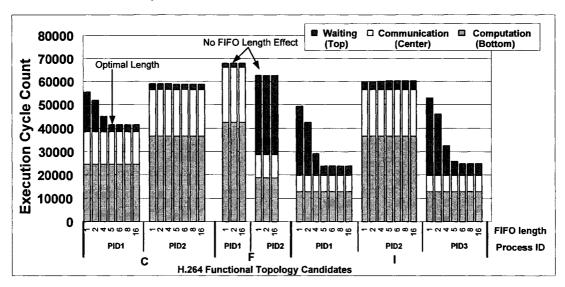

| 5.9  | METROPOLIS H.264 Simulation Results for Various FIFO Sizes           | 152 |

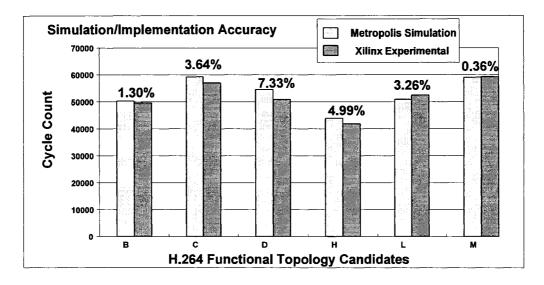

| 5.10 | METROPOLIS H.264 Accuracy Versus FPGA Implementation                 | 154 |

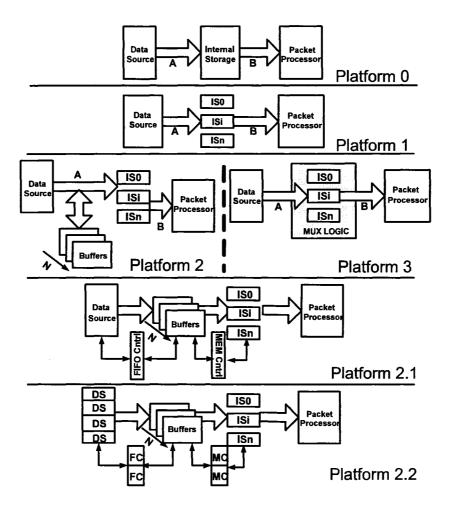

| 5.11 | Successive Platform Refinement Methodology                           | 158 |

| 5.12 | Platform Development for SPI-5                                       | 159 |

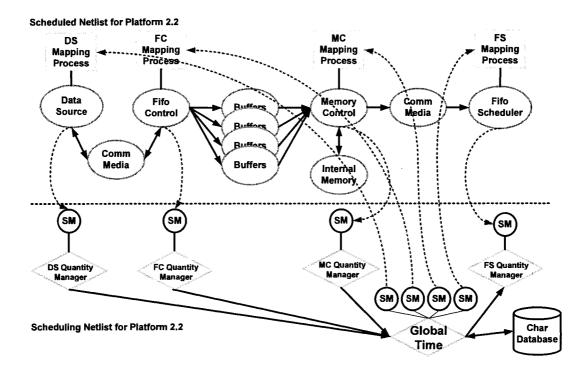

| 5.13 | METROPOLIS Architecture Model for Platform 2.2                       | 163 |

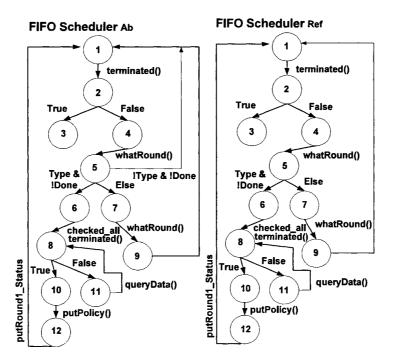

| 5.14 | Sample Control Flow Automata for Abstract and Refined FIFO Scheduler | 164 |

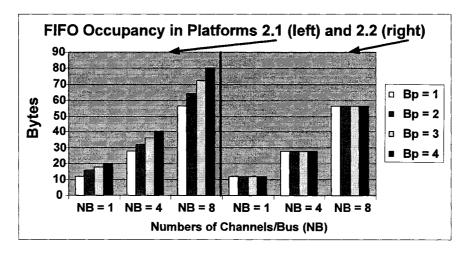

| 5.15 | FIFO Occupancy Data for Platform 2.1 and 2.2                         | 165 |

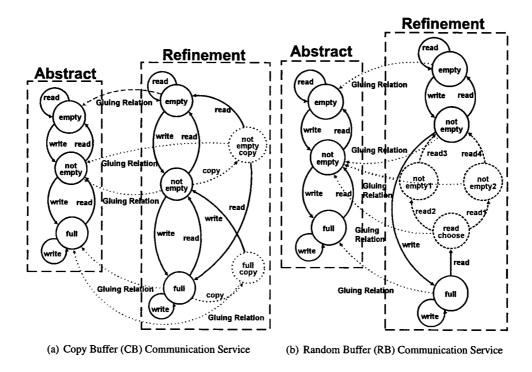

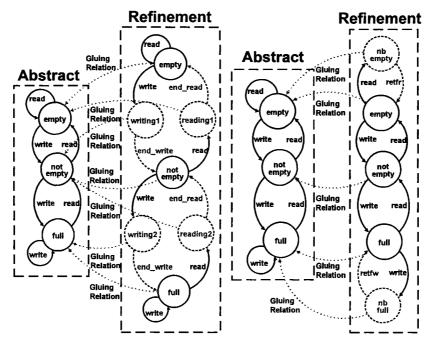

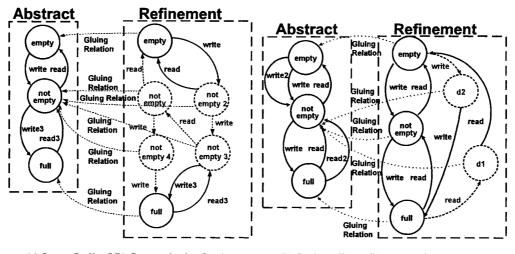

| 5.16 | LTS Communication Example #1 for FLEET                               | 167 |

| 5.17 | LTS Communication Example #2 for FLEET                               | 168 |

| 5.18 | LTS Communication Example #3 for FLEET                               | 169 |

| 5.19 | FLEET System Architecture Service Refinement Opportunities           | 170 |

| 5.20 | LTS for Entire FLEET System Level Service Models                     | 172 |

## **List of Tables**

| 1.1 | Relationship Between Factors, Solutions, Supporting Techniques, and Outcomes       | 5   |

|-----|------------------------------------------------------------------------------------|-----|

| 1.2 | Characteristics of Programmable Platforms                                          | 18  |

| 1.3 | Programmable Platform Technology Classification                                    | 18  |

| 1.4 | Example Programmable Platform Architecture Classifications                         | 19  |

| 1.5 | Horizontal/Vertical Axis Classification Example [Pat01]                            | 19  |

| 1.6 | Contributions of this Thesis                                                       | 23  |

| 2.1 | Comparison of Architecture Service Modeling Approaches                             | 34  |

| 2.2 | PowerPC store instructions                                                         | 54  |

| 2.3 | PowerPC load instructions                                                          | 54  |

| 2.4 | PowerPC Service Performance Estimation Summary                                     | 54  |

| 2.5 | MicroBlaze Service Performance Estimation Summary                                  | 55  |

| 2.6 | PLB Bus Service Performance Estimation Summary                                     | 58  |

| 2.7 | OPB Bus Service Performance Estimation Summary                                     | 59  |

| 2.8 | Memory Service Performance Estimation Summary                                      | 61  |

| 3.1 | Performance Characterization Tradeoffs                                             |     |

| 3.2 | Example CoreConnect Based System Permutations for Characterization                 |     |

| 3.3 | Non-linear Performance Observed in PPC Systems                                     |     |

| 3.4 | Sample Simulation Using Characterization Data                                      | 79  |

| 4.1 | Refinement Verification Related Work Classification                                |     |

| 4.2 | Potential Vertical Refinement Event Traces                                         |     |

| 4.3 | Potential Horizontal Refinement Event Traces                                       |     |

| 4.4 | Resource Utilization Event Analysis                                                |     |

| 4.5 | Latency Event Analysis                                                             |     |

| 4.6 | Asymptotic Analysis of Surface Refinement Flows                                    | 132 |

| 5.1 | MJPEG Encoding Simulation Performance Analysis                                     |     |

| 5.2 | H.264 Performance and Cost Results for All Topologies                              |     |

| 5.3 | Example of SPI-5 Data Generation Using the Architecture and Application Parameters | 156 |

| 5.4 | SPI-5 Application Parameter Interaction                                            |     |

| 5.5 | Traces from FIFO Scheduler CFAs                                                    | 165 |

| 5.6 | FLEET LTS States and Transitions                                                   | 173 |

|     |                                                                                    |     |

#### Acknowledgments

I would first like to thank my advisor Alberto Sangiovanni-Vincentelli. Not only for his support in helping me to complete this thesis (and by implication my graduate student career), but also for his mentorship, advice, and leadership. As I go forward in my career I will forever benefit from our interaction and I hope that I can be an example to other students some day as he was to me.

Naturally I need to acknowledge all the wonderful fellow graduate students I have worked with over the past 6+ years while at Berkeley. In particular Abhijit Davare, Qi Zhu, Trevor Meyerowitz, Alessandro Pinto, Guang Yang, Mark McKelvin, Donald Chai, Matt Moskewicz, and Will Plishker. I enjoyed our many interactions both academic and otherwise. I look forward to when our paths cross again. Best of luck in all your future endeavors.

Additionally, although not listed explicitly here, all the residents of the Donald O. Peterson (DOP) Center (Alberto's group in particular), many other EECS graduate students, and Berkeley students in general were a pleasure to spend time with. I wish them all the best not only in their studies but in all aspects of their life. Hopefully we will one day realize what an honor it was to study at a place like Berkeley. It is impossible to list everyone important to me here. In the event of an omission, know that you are still in my heart.

As a UC Berkeley graduate student I have had the pleasure of working with some of the best researchers in the world. My discussions with Ivan Sutherland, Yoshi Watanabe, Shinjiro Kakita, Samar Abdi, Felice Balarin, Luciano Lavagno, Marly Roncken, John Moondanos, Jason Cong, Adam Donlin, Patrick Lysaght, John Wawrzynek, Dan Garcia, Edward Lee, and David Patterson were truly inspirational and I am a better person as a result of our interaction. Thanks for the doors you opened and continue to open for me both in terms of my career and intellectually.

As every researcher knows, nothing gets done without a tremendous support staff. The Berkeley staff and administrators such as Sheila Humphreys, Colette Patt, Ruth Gjerde, Mary Byrnes, Beatriz Lopez-Flores, Loretta Lutcher, and Carla Trujillo gave Berkeley a human touch and on some level they are the reason that I came to Berkeley. They are extremely dedicated folks and a true asset to the university. Thanks for everything!

While at Berkeley I was involved in various student groups such as BGESS, LAGSES and HKN. Fellow members of these groups such as Noaa Avital, Kofi Boakye, Nerayo Neclemariam, Lisa Angus, Fabian Beltran, Esther Zeledon, Rey Guerra, Hakim Weatherspoon (Makda and the kids too), Rob Crockett, and Greg Lawrence provided the extra laugh or pat on the back that made all the difference.

A number of companies have supported me throughout the years as well. Intel in particular has

been amazing providing me with 4 internships and two fellowships. They gave me a chance when I was a 20 year old sophomore with little experience. Without this co-op experience I would not have had the confidence to know that I could be a successful engineer. Xilinx and Cypress semiconductor as well have been open to my research and supported me during internships and provided me with equipment during my time as a grad student. Cadence Berkeley Lab was also vital in my early development as a researcher.

Naturally I am indebted to other my other readers as well. Prof. Jan Rabaey's and Prof. Lee Schruben's participation in both my qualifying exam as well as the thesis process in general was much appreciated and I hope that you both found the process both educational and interesting. Best of luck in all your future goals both personal and academic. A special thanks to Jan for dealing with my crazy "signature issues".

I want to thank the various students that I mentored during my time at Berkeley as well. Murphy Gant, Rhishi Limaye, Alex Elium, Jue Sun, and Rodny Rodriguez all helped me to learn what I do well and what I need to work on regarding my teaching and mentoring skills. Aspects of our collaborations are part of this work! I hope you learned one half of what I learned from you all. Also my time mentoring lyibo Jack from the University of Washington was extremely beneficial as well.

As any student will tell you, a strong networks of friends is vital to complete any PhD program. My undergrad crew of Dale Winling, Neel Varde, Chris Burke, Jake Montgomery and Ryan Owen gave me a reason to look forward to August for the past 6 years (one day it will be Mock 10!). Of course, Steve Berke, Moses Morales, and Nils Hernandez have been my "California peoples" since 1998. Who would have thought almost ten years later we would still be in touch. Patrick Collins opened up my eyes to a lot of things in life and just plain showed me how to relax a little. I can't think of a better roommate in the world and congratulations on the engagement. "That serum is raw"!

Over the past 11 years of my college experience, I have far too often had to put school ahead of my family. I hope to remedy this in the future. Mom and Dad, thanks for instilling in me the values, perseverance, and wisdom needed to complete my studies. Diana, Luke, and Kate, please keep following your own dreams and know that while I have achieved some measure of success, it pales in comparison to what you can achieve. You all are so talented. To Matt, Alyson, and the boys, I look forward to establishing a better relationship with you all as I transition into my "adult life" as a married man. I miss you all, and can't wait to see you all back in Michigan!

Finalmente tengo que decirle algo a la persona más importante en mi vida. Erika, tú eres la razón por la que me despierto en las mañanas y quiero mejorarme. La razón por la que cuando no quiero continuar, me doy cuenta que la vida es mucho más que la ingeniera y que todo va a estar bien contigo. Gracias por tu paciencia, amor, y amistad.

### Chapter 1

### Introduction

"The perfect computer has been developed. You just feed in your problems and they never come out again." - Al Goodman

The Electronic Design Automation (EDA) industry is currently experiencing a slow down in growth. This slow down ranged from 1% [Jay05] to -0.6% [Gar05b] growth in 2005 and only 3% [Jay05] growth in 2006. This data is down from a growth spike of 7.6% in 2001 [Lau02]. In order to counteract this slowdown, companies (both established and new) are looking to exploit new business opportunities. In previous years, tools were able to make incremental improvements to their approaches and designers were able to use existing and traditional design flows to produce products successfully (on time and at a profit). The success of these small improvements was able to sustain growth. Many analysts feel that this incremental process will not be possible in the future [Peg06]. A change in the EDA industry will have to occur for this segment to grow and thrive. This change must be systematic and across the entire industry in order to be truly effective. Designers are going to have to shift to a new way of not only designing systems but also to new ways of thinking about the design process.

One of these new business opportunities is in Electronic System Level (ESL) design tool and methodology development. According to the International Technology Roadmap for Semiconductors (ITRS) in 2004 [Int04b] ESL is defined as "a level above RTL including both HW and SW design". ESL is defined to "consist of a behavioral level (before HW/SW partitioning) and architectural level (after HW/SW partitioning)" and is claimed to increase productivity by roughly 200K gates/designer-year. The ITRS states that ESL will produce an estimated 60% productivity improvement over what they call "intelligent testbench" approaches (the previously proposed ITRS electronic system design improvement). While these claims cannot be verified as yet and do look quite aggressive, most agree that the overaching benefits of ESL are to:

• Raise the level of abstraction at which designers express systems;

- Enable new levels of design reuse;

- Provide for design chain integration across tool flows and abstraction levels.

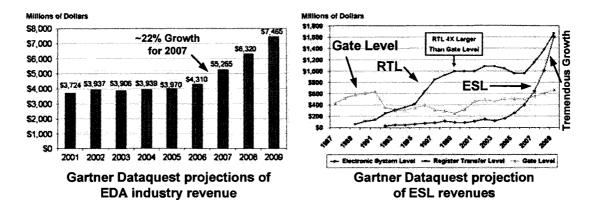

As a direct result of ESL tool introduction, EDA growth is predicted to be 22% [Ric05] in 2007! Figure 1.1 shows not only the impact ESL will have on increasing EDA growth in the future (in terms of overall revenue projections), but it also shows how ESL tools are predicted to rival RTL tools (Register Transfer Level; usually specifying a relatively low abstraction level) in terms of revenue potential. This trend is very important as RTL is the current design benchmark in EDA.

Figure 1.1: Overall EDA Revenue Growth and EDA Design Segment Growth [Ric05]

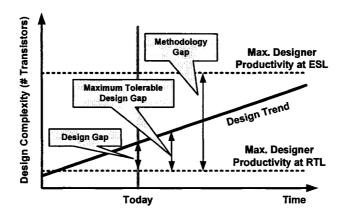

ESL methodologies and tools are of increasing interest because they specifically look to exploit the "design gap" experienced by current design flows. More accurately this should be termed a "methodology gap" which exists between old design methodologies (i.e. RTL) and new design methodologies (i.e. ESL). Figure 1.2 presents a qualitative graph relating design complexity to designer productivity with both RTL and ESL design methods. Today, most designers work with RTL design tools and languages (VHDL and Verilog for example). They find themselves in the "methodology gap" where the system they are trying to create exceeds the capabilities of their design environment. This is not to say that the methodology gap cannot be crossed. On the contrary, the gap can be overcome with existing design methods but only at a significantly increased cost (both financially and in designer effort). Existing RTL design methods will continue to be employed until the additional cost of design overwhelms the commercial viability of the final design. This "maximum tolerable design gap" as shown in Figure 1.2 varies per technology, per market segment, or even per product and is always present at some level.

Figure 1.2: "Methodology Gap" Challenge in EDA

A transition from RTL to ESL is required to completely overcome the "methodology gap". A transition must occur since it is well accepted that design complexity will continue to increase (reflected in the continuance of Moore's Law). Today, the design community is approaching a point of inflection between the two methods - the rate of ASIC design starts in recent years has remained flat while implementation/programmable technology's growth has continued to trend upwards [Gar08]. An important question, therefore, is "what limits the widespread adoption of ESL by the majority of designers?". A simplistic answer is that ESL design methods, tools, and languages are simply not mature enough to convince designers to risk traversing the gap between the two methodologies. To further complicate the answer, we must respect that ESL methods must tackle multiple design problems. It is ultimately the design projects itself which influences the relative importance of each problem. Therefore, a complex compromise must be struck between the ESL vendors who create a set of tools and the system designers who must work in ESL environments.

Because of the potential to bridge the "methodology gap", ESL is being widely adopted and there have been a number of industrial tools and academic tools created to be ESL based solutions. While this thesis will not cover the entire space of these tools or provide a taxonomy of these approaches, [Dou06c] does provide a comprehensive taxonomy and the reader is invited to examine this work. That taxonomy exposes the fact that there are many contributions. Each approach attempts to solve a variety of design problems. However, there is by no means a unified view of how to best attack the forces driving ESL development. Fortunately there are a number of design scenarios which ultimately dictate which methodology is employed. A major contribution of that taxonomy is that it clearly demonstrates that all tools can be categorized around three orthogonal design aspects:

**Definition 1.0.1 Functionality** - this is "what" a system does. This can also be considered the application the design implements. Other common terms for this area are application domain or behavior.

Definition 1.0.2 Architecture - this is "how" a system carries out its operation. This can also be considered the services the system provides. Other terms for this area are platform components or services. Note that this can be traditional HW ASIC components, programmable processing engines, as well as general purpose processors (GPPs) capable of running software. All of this development is subject to abstraction in which case architecture services could be anything from logic gates to ISA instructions. The development of architecture service models in this area is the focus of this thesis.

**Definition 1.0.3 Mapping** - this is the process of assigning functionality to architecture (behavior to services). Often this is called binding as well and is traditionally seen as part of the synthesis process. This an assignment between behaviors in the functional model and services in the architectural model. Mapping can be "many-to-one". This allows "many" functional behaviors to be assigned to "one" architectural service. For example a DCT and FFT behavior can be mapped to a single abstract service dealing with signal processing.

There is a great deal of work related to each of these three areas as was shown in the taxonomy work [Dou06c]. Often ESL tools will fall into one of these categories only or perhaps combinations. The areas themselves will be touched on more specifically in Section 1.2 when System Level Design (a methodology within ESL) is described in more depth. It should be pointed out again that this thesis in general will focus on architecture service model development for ESL. This thesis will demonstrate how embedded system architecture service models can be created and how to formally verify properties of these models as it relates to refinement.

At this point is should be made very clear that this work is of interest since in order to legitimize ESL and to continue its adoption, architecture service modeling will need to be provided in such a way that various desired ESL characteristics attributed to abstraction can be maintained while achieving performance goals associated with RTL. Specifically this thesis will:

Demonstrate that architecture service modeling in system level design (SLD) can allow abstraction and modularity while maintaining accuracy and efficiency.

Abstraction allows the system to be described early and at a reasonable cost but it also casts a shadow of doubt over the accuracy of performance analysis data. Since the data gathered during simulation guide the selection of one system architecture over another, the veracity of data recovered from ESL

performance analysis techniques with respect to the system feature being investigated must be considered carefully by the designer. Fear of inaccuracy in ESL performance analysis is a major impediment to the transition from RTL to ESL. Preventing this inaccuracy is paramount for ESL acceptance and legitimacy and is the major goal of this thesis.

Modularity encourages reuse, localizes system functionality, provides more system observability, and helps to manage complex system development. However modularity can often be at odds with simulation efficiency. Overheads often associated with modularity may decrease simulation speed or enforce rigid syntactic or semantic requirements on the designer. If a design environment is to be widely accepted it must remain equally efficient (if not more so) as the current design environments it is replacing for the same amount of design productivity gains (both in terms of design time saved and design space explored). Preventing this inefficiency is also paramount for ESL acceptance and legitimacy and is partner to accuracy as a goal of this thesis.

To these ends, the goals of this thesis are outlined in Table 1.1. This table shows how environmental and industrial factors (Heterogeneity and Complexity) lead to the solutions (Modularity and Abstraction) that a ESL methodology should achieve. This thesis provides the techniques listed to achieve these goals and produce the stated outcomes (Accuracy and Efficiency). This is the central proposition of all of the work contained in this thesis.

| Factor        | Solutions                                                                       | Supporting Techniques                                    | Outcomes   |

|---------------|---------------------------------------------------------------------------------|----------------------------------------------------------|------------|

| Heterogeneity | erogeneity   Modularity   Event Based Architecture Service Modeling (Chapter 2) |                                                          | Accuracy   |

|               |                                                                                 | Architecture Service Characterization (Chapter 3)        |            |

| Complexity    | Abstraction                                                                     | Architecture Service Refinement Verification (Chapter 4) | Efficiency |

Table 1.1: Relationship Between Factors, Solutions, Supporting Techniques, and Outcomes

#### 1.0.1 Chapter Organization

The rest of this introductory chapter will provide a more in depth analysis of the current industrial design environment and this thesis' contributions toward addressing these issues. First in Section 1.1, a more in-depth discussion of ESL's (and hence this thesis') motivating factors will be covered. Section 1.2 will introduce the reader to the System Level Design methodology within ESL and more specifically to the METROPOLIS design environment which will be used primarily to demonstrate the techniques outlined. Section 1.3 will introduce the reader to programmable platforms and the powerful role they will play in architecture service modeling. Finally Section 1.4 will introduce the contribution this thesis makes to the

area of ESL in the form of a complete design flow. It will outline a naïve design flow approach and close the chapter with the improved proposed design flow which will be discussed throughout this thesis.

#### 1.1 Motivating Factors

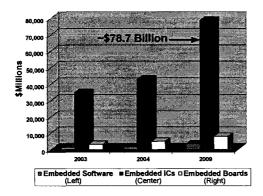

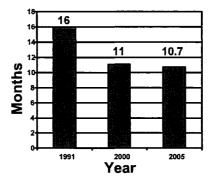

There is a great deal of financial commitment and human resource effort involved in EDA. In 2005 the revenue in EDA was 3.9 billion dollars and was 4.3 billion dollars in 2006. It is projected as being as high as 7.4 billion dollars in 2009 [Ric05]. According to [Rav05] the embedded hardware market (which uses EDA tools) will reach \$78.7 billion in 2009 assuming an aggregate 14.2% growth rate. Figure 1.3 illustrates this tremendous growth of embedded integrated circuits, software, and printed circuit boards. This information clearly shows it is a very costly proposition to begin the process of shifting the entire industry to a new design methodology. It is not done on a whim or due to passing marketing pressures. The slow down in growth mentioned previously in the introduction however has started the migration process to ESL and it appears that there is no turning back. The migration to a new methodology is very cognisant of and concerned primarily with four key factors. The first factor is heterogeneity in device types, systems fabrics, and technologies. The second factor is *complexity* both in application and architecture designs. The third factor is time to market pressures. In semiconductor design for example, the design cycle times have decreased 33% since the early 1990's [Gar05a]. A sampling of design cycle time decline is shown in Figure 1.4. This trend means that designs must avoid long development cycles and developer iterations in order to see profits necessary to justify new product development. The final factors are involved in nanometer era design effects and are not discussed in this thesis (but mentioned since they deserve recognition). This thesis focuses in next three sections on the first three factors in more detail. These factors are what will lead to the solutions outlined in Table 1.1 and ultimately the techniques upon which this thesis is based.

#### 1.1.1 Heterogeneity

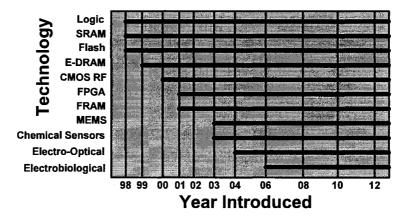

Heterogeneity is defined as "the quality or state of being heterogeneous" where heterogeneous is defined as "consisting of dissimilar or diverse ingredients or constituents" [Mer06]. In the case of embedded system design and electronic system design in general, there are primarily two broad classes of heterogeneity. The first class deals with the various technologies integrated on a printed circuit board (PCB) or even the device die itself. Figure 1.5 shows "Existing and Predicted First Integration of SoC Technologies with Standard CMOS Processes". Notice by the release date of this thesis (Spring 2007), all 11 of the presented technologies have been introduced. These technologies range all the way from basic CMOS logic to chem-

Figure 1.3: Global Embedded Systems Market [Rav05]

Figure 1.4: Semiconductor Design Cycle Time Decline [Gar05a]

ical sensors and electrobiological components. In order to make sure that these devices function properly, models must be created which can capture the complex interactions caused by such diverse combinations. As nano-technology continues to be developed [Cha03] it is clear that integration heterogeneity issues will only continue to become more complex and critical.

Figure 1.5: Technological SoC Heterogeneity [Don04]

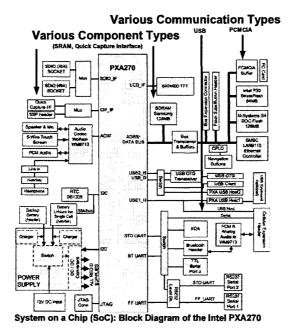

The second type of heterogeneity is inter-device heterogeneity. This description speaks to the many different types of individual components that are often assembled in a design (often on a single die). Figure 1.6 shows the Intel PXA270 System on a Chip (SoC). This integrated circuit is used in such devices as the Mypal A730 Personal Digital Assistant. This PDA has many state of the art features and is equipped with a digital camera and a VGA-TFT display. The primary issue in these types of systems is making sure

that the communication between individual components can be sufficiently captured during simulation so that not only system functionality can be verified during design but also that debugging is manageable. One must be able to isolate communication from computation, deal with different data types, and different timing domains. Also it is important that each component be designed separately so that various product families can be developed with these components to service markets with different performance, power, and price requirements.

Figure 1.6: Device Component and Communication Heterogeneity [Int06b]

Heterogeneity is a factor that is not only difficult to manage but is increasingly becoming required. It is not practical or possible to have homogeneous systems for today's applications and in many cases the presence of heterogeneity may be seen as a design's strength. From this key design factor comes the first solution of this thesis: **Modularity**.

**Definition 1.1.1 Modularity** - the ability to define clearly the boundary between interacting components both in terms of their communication, computation, and coordination. At these boundaries, components should be able to be tested and verified for correct functionality. In addition, there should be rules regarding how systems are composed of these components and how those boundaries can be changed during refinement.

If a design is modular, one can test its components in isolation and will allow for reuse. Modularity allows communication issues to be isolated from computation issues as well. Throughout this thesis, modularity will be emphasized as it is a critical contribution in the design of system level architecture service simulation and verification techniques. Modularity will be constantly monitored in the context of maintaining an efficient simulation environment.

#### 1.1.2 Complexity

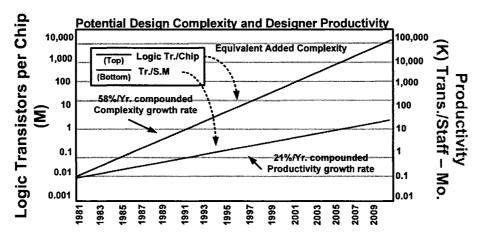

The second factor influencing the development of system level design methodologies is the increasing complexity seen both at the application level as well as how many devices can be introduced on a die. Moores law fuels much of this progress on the technology side but applications are increasingly requiring more memory and compute power. Multimedia applications are an excellent example of this phenomenon. IBM's cell processor [Jim05] (an example of a cutting edge architecture design) is prominently featured in the Sony Playstation 3 and the most sophisticated devices in PCs today are related to graphics processing for videogames [Nol05]. Figure 1.7 provides a very clear illustration of the issues these complexity trends introduce. One of these is the increasing complexity of designs as measured by the number of transistors present in a device. This figure shows a 58% per year compounded complexity growth rate. However, the productivity rate (as measured in transistors per staff month) is only increasing at a 21% compounded growth rate. This growth rate mismatch leads to an increasing productivity gap (this manifests itself as the "methodology gap" discussed earlier). There is no inherent problem with the producvity gap. In theory this just means that all of the power of a device will not be realized. However in practice this gap leads to at least two side effects. The first effect is that in the quest to utilze all that complexity, designs end up taking more time to develop. This is due to the fact that new architectural innovations must occur in order to take advantage of the added silicon. In the case of general purpose processors for example, companies like Intel are no longer pursuing advanced superscalar techniques but rather looking a multi- and many-core devices. These designs bring with them a whole set of verfication, test, and design difficulties. In the event that productivity can not keep pace it is very likely that design times will dramatically increase. This translates into lost revenue and lost opportunities for many companies. In order to prevent this, the second effect is seen. Companies often respond by increasing the number of employees to tackle this problem. This leads to more development costs which end up raising the cost of the device. It is also not clear that this is simply a manpower issue. It is possible that more manpower will only exacerbate the complexity and management problem. In the event that the market will not bare this increased cost either the employees cannot be hired or companies are not as profitable. Often what this means is that only the largest companies are able to compete in this space and as a result creativity and competition are not promoted. Innovation cannot occur and the small companies which may be ideally placed to look at new ideas are not viable!

Figure 1.7: Growing Gap Between Device Capacity and Designer Productivity [Int99]

As heterogeneity was coupled with modularity, the complexity factor is coupled with the solution of design **Abstraction**.

**Definition 1.1.2 Abstraction** - the addition of system behaviors. A system is more abstract if it has more possible behaviors and less abstract if it has fewer possible behaviors. Abstraction does not have to do with code size, complexity of execution, or number of "details". Abstraction can be seen as a relaxation of constraints which expands the space of behaviors a system can exhibit. It is the process of obscuring aspects of the design in order increase the ability of the designer to only consider those which help to develop a design at that particular stage.

Abstraction could be a set of transistors being represented as logic gates, a set of bus transactions being reduced to a IP interface, or the operation of a processor being a set of abstract services (add, divide, etc). Abstraction will allow more device resources to be utilized more easily but it must be tempered by the level of controllability, observability, and accuracy. Higher levels of abstraction allow design changes to most dramatically effect the overall design but a designer also has the least insight into how precisely the changes brought about this change. The inverse is true for less abstraction. What is needed is something with the best of both techniques. This thesis will show how abstraction can be achieved while maintaining

accuracy. Specifically maintaining relative accuracy or fidelity.

**Definition 1.1.3 Fidelity** - requires that all pairs of corresponding measurements  $m_1$ ,  $m_2$  in a abstract model and  $p_1$ ,  $p_2$  on the actual implementation, hold  $m_1 < m_2$  if and only if  $p_1 < p_2$ .

#### 1.1.3 Time to Market

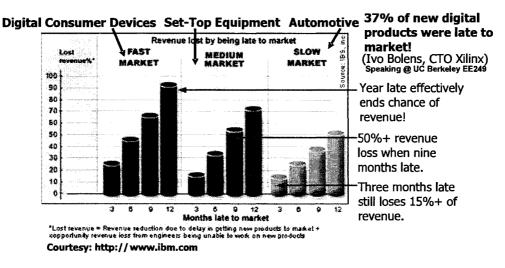

The first two factors, heterogeneity and complexity, were aspects of embedded system designs that were technology and application driven. The final factor, time to market pressure, is consumer driven and is **in opposition** to the other factors. Time to market is *why* a design method needs to be **accurate and efficient**. If it is not, there will be long iterations in the design and as a consequence release dates will slip. Figure 1.8 shows three markets described by what the industry norm is regarding time between subsequent product releases (fast, medium, and slow). These markets could represent digital consumer devices (PDAs, cell phones), set-top equipment (televisions, DVD players), and automotive industries respectively. The Y-axis is what percent of revenue is lost if you are N months late (X-axis). While this is a fairly qualitative figure, the spirit of it remains. Essentially any longer than 12 months late is considered a product failure from a revenue standpoint. As little as 3 months late can be drastic as well (potentially losing as much as 15% of the expected product revenue). The lesson learned here is that time to market windows are small and the financial cost of missing them is extremely high.

Figure 1.8: Time to Market Revenue Consequences [IBM06]

Time to market issues cannot be ignored since it they are why companies cannot take an arbitrary amount of time to produce designs. Granted it is not the only factor calling for an efficient design process (for example it would not be cost effective to manufacture an arbitrary number of devices at any design process speed in order to weed out process errors) but it is nonetheless a very powerful factor and the underlying influence behind almost all EDA efforts (tool design by nature looks to speed up the design process since time is often equated with designer effort).

#### 1.2 1st Focus: System Level Design

The beginning of this chapter discussed Electronic System Level (ESL) design and its increasingly important role in EDA. Often an approach within ESL concerned with specific system wide integration goals (reuse, modularity, formal techniques) is called System Level Design (SLD) [Kur00] (often ESL and SLD are used interchangeably). SLD allows for a designer to think of traditional software and hardware aspects of the design separately. Algorithms are decoupled from the elements which implement them. For the purposes of this thesis, system level design is going to refer primarily to the level of abstraction employed. Computation will take place at the granularity of function calls typically. Communication operations will be considered as transactions (as opposed to bit-level or register interactions).

**Definition 1.2.1 System Level Design** - a design methodology whereby the interactions amongst components at an increased abstraction level are examined. Design is done taking the entire system into consideration as well, not just individual components.

It is important to understand that SLD is a large design umbrella defined by a generic set of goals with a number of various approaches possible within ESL. In fact within ESL there are many industrial and academic offerings with claims to be members of the SLD community. In [Dou06c] (the taxonomy previously mentioned), over 90 tools and environments were categorized. The approaches differed by their ability to support (F)unctional modeling, (P)latform services, or (M)apping capabilities. Approaches could be combinations of these distinctions. If this thesis work is to use the terminology used in that source, then specifically it will examine an FPM approach. FPM approaches are attractive since this thesis investigation could be carried out in one unified environment. In particular this thesis will be focusing in on a particular style within ESL called, *Platform-Based Design* [Alb02]. Platform-Based Design (PBD) is concerned with what is termed the *orthogonalization of concerns*. These concerns are:

• Functionality (what something does) and Architecture (how it does it). For example multiplication

itself is very well defined functionally. However, the architecture which implements it may be a series of adders or a dedicated multiplier. This separation goal is shared by a variety of other SLD methodologies.

- Behavior (Semantics) and Performance Indices (Latency, Throughput, etc). Behavior defines how a

device operates. A bus protocol is an example of a behavior. Performance is a cost of that behavior. Bus transaction latency times (performance) are a function of many things not specified by the

behavior (for example clock speed is not a behavior).

- Computation, Communication, Coordination. How things compute should be separate from how they

interact (communicate) with other aspects of the system, and both computation and communication

should be separate from the scheduling mechanisms.

By keeping these issues separate, the now modular design allows for a smoother verification process, reuse, and abstraction. These are exactly elements that were stated as goals of this thesis!

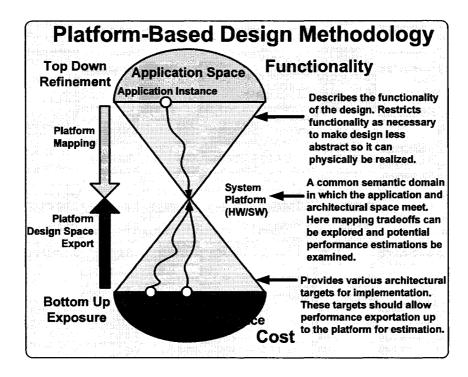

In order to achieve these goals, PBD is a three stage process: top down application development, bottom up performance exposure, and defining a common semantic meeting point to explore functionality and architecture mappings. Figure 1.9 illustrates this methodology and provides the needed description.

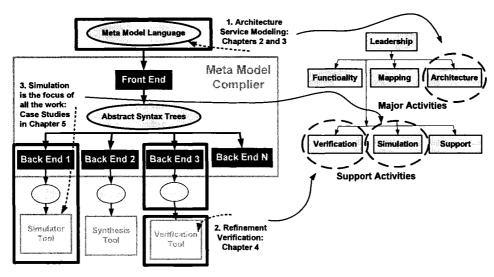

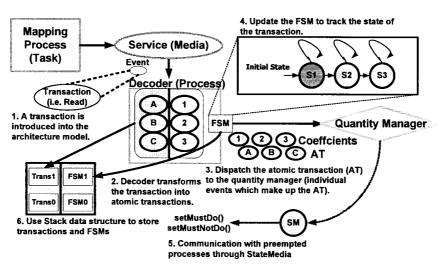

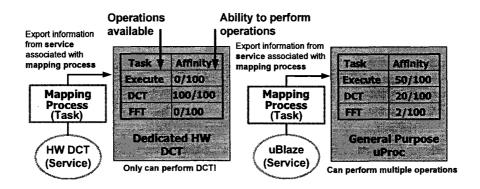

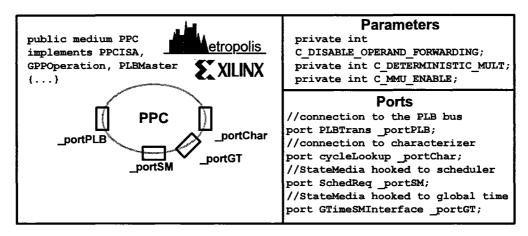

An ESL tool using a Platform-Based Design methodology is METROPOLIS [Fel03]. As mentioned, METROPOLIS is an FPM (Functionality, Platform, and Mapping) ESL solution. It is developed at UC Berkeley and is available through the Gigascale Systems Research Center (GSRC). The design environment is shown in Figure 1.10 along with its organizational structure in terms of primary and support activities. The beginning of a METROPOLIS design flow starts by describing either a functional model or architectural model in the METROPOLIS Meta-Model (MMM) language. Working at the MMM level to develop architecture service models will be the scope of the discussion in Chapters 2 and 3. From this user input, the Meta-Model compiler decomposes the description into an abstract syntax tree (AST). This AST can be fed into any number of backends in order to simulate the design, perform synthesis, or for verification tasks. The majority of this thesis is interested in using METROPOLIS for design space exploration (DSE). Chapter 4 will include a discussion of how backends can be used to verify refinements of architecture services.

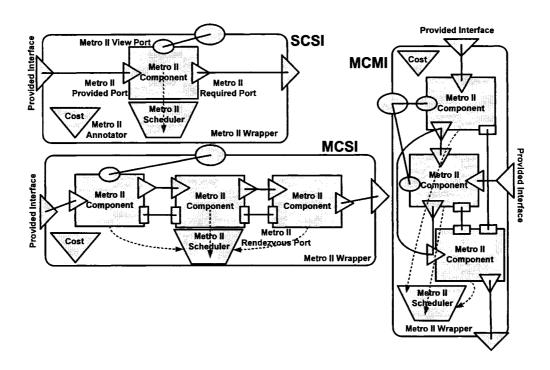

Another ESL tool using Platform-Based Design is METRO II. Also an FPM based approach, it is the successor to METROPOLIS. Primarily it looks to streamline METROPOLIS and provide better support for heterogeneous IP import, cleaner separation of annotation and scheduling activities, and a three phase simulation engine. Chapter 2 will provide a proposal on how architecture service models may be modeled using this tool.

Figure 1.9: Platform-Based Design Methodology [Alb02]

**Definition 1.2.2 Design Space Exploration** - the process of looking at a variety of designs and using the results of simulation, verification, or other analysis methods to make decisions regarding which design should be selected, which modifications can be made to existing designs to increase performance, and observe potential design issues that may have been overlooked during specification. This process is done prior to committing to a particular design with the intention of physically creating it or its prototypes.

Chapters 2 and 3 will discuss how models can be developed for DSE. Chapter 4 will utilize a backend for verification which be used in conjunction with simulation to make guarantees about design correctness during DSE. Chapter 5 will provide a number of case studies to demonstrate the applicability of the techniques proposed.

It should be noted that this thesis is independent of METROPOLIS or METRO II. It is true that there are aspects of these environments exploited to achieve the goals outlined previously. However these can be applied to other tools as well. More specifically, a design environment with the following characteristics would also be able to take advantage of the techniques outlined by this thesis:

- 1. Support for multiple models of computation this thesis requires both tagged signal modeling semantics as well as data flow modeling.

- 2. Explicitly separate an architecture model's behavior and how its operation is scheduled this thesis requires this separation to meet its performance and reuse goals. The refinement formulation is also highly dependent on this distinction.

- 3. Event based synchronization this thesis requires that elements which form architecture services be coordinated with events.

More specifics about METROPOLIS and METRO II execution and modeling will be covered in Chapter 2 and can be found in [Fel03] and [Abh07].

Figure 1.10: METROPOLIS Design Environment and Organization

#### 1.3 2nd Focus: Programmable Architecture Services

When having a discussion about creating abstract, modular architecture service models which are still efficient and accurate one must quickly determine what types of implementation devices one is going to consider. One could consider static architecture service models. A static architecture service model for the purposes of this thesis is one which has its functionality bound during manufacturing. This is the case when speaking about a General Purpose Processors (GPP) such as Intel's Pentium 4 [Int06a] or ARM

style processor [ARM06]. ASIC designs could also be members of this group. These devices are perhaps programmable at the ISA level (GPPs) but one cannot change the computation fabric or interaction between computation or communication units after fabrication. The are usually either very special purpose (ASICs) or very generic (GPPs). Often they have a high design cost but are often cheaper to manufacture and recoup that design cost in sales volume. At the other end of the spectrum are programmable architectures or platforms (the term platform denoting a set of services which typically are not associated with traditional CPU architectures). A programmable platform is a system for implementing an electronic design. Examples of these are Platform FPGAs and ASIPs. These systems are distinguished by their ability to be programmed regarding their computation (functionality), communication (topology), or coordination (scheduling). Programmable platforms are increasing in use and popularity for several reasons: [Kur02], [And00]

- Rapid Time-to-Market One can often eliminate fabrication time by using off the shelf parts. This also bypasses a large part of the verification time as well since parts are well understood and there is no post silicon verification phase.

- Versatility, Flexibility (increase product lifespan) Design reuse within a programmable architecture family is often possible.

- In-Field Upgradeability Many devices are reprogrammable using as little as a personal computer or a portable flash memory card.

- **Performance**: 2-100x compared to GPPs Special purpose computation units can exploit spatial concurrency or dedicated hardware can be created.

Table 1.2 lists a set of characteristics that allow programmable platforms to achieve those advantages. However they naturally have some disadvantages as well:

- **Performance**: 2-6x slower than ASICs Programmable architecture topology overhead related to programming the device may hurt performance. For example, FPGAs are unable to perform routing as efficiently as a custom ASIC due to its mesh like structure.

- Power: 13x compared to ASICs Programmable architecture fabric is not typically optimized for power although companies are starting to improve their power consumption dramatically.

Overall the strengths outweigh the weakness as both of the weaknesses are becoming less of an issue as technologies mature. Programmable Platforms often have a very regular device fabrics (FPGAs for example are famous for this). This regularity allows for advances in device technology (such as transistor

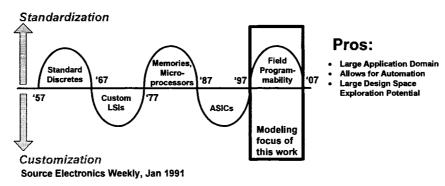

scaling) to be taken advantage of with minimal design changes. An FPGA is able to double its computing capacity every 18 months with the same die size potentially. In fact, industry luminary Tsugio Makimoto of Sony Corporation has programmable platforms as a key extension of his now famous "Makimoto's Wave". Figure 1.11 illustrates this point. The wave demonstrates the observation that the electronics industry oscillates between standardization and customization. Standardization is used to proliferate designs and enable new companies and designers to enter into the marketplace. Customization occurs as a means for innovation and to enter new market areas where standards are not in place. Standardization is able to take advantage of factors such as regularity, automation, and predictability. All of those factors are reasons why this thesis explores programmable architectures services (a standardized approach). Tool development by its very nature is most productive during the standardization cycle of the wave.

#### **Makimoto's Wave**

Figure 1.11: Makimoto's Wave and Programmable Devices [Tsu00]

Because of their increasing relevance and prevalence, programmable platforms are a natural target for ESL design flows. In addition, they directly target time to market issues. Also they often side step technology heterogeneity issues since they have regular design fabrics. Finally, they can be customized to directly address new complex applications. From a practical standpoint, if one were to create architectural models of a programmable device, these models by definition could be used to represent a very large set of individual architecture instances (i.e. each configuration). By modeling the primitives of the programmable platform a very large design space can be easily created from a relatively small model set. However it is not enough to say that this thesis will focus on programmable platforms since this is still a broad classification. The discussion will now begin the process of narrowing down the focus within this space.

To begin, the characteristics of programmable platforms are shown in Table 1.2. These characteristics are intentionally vague and meant to contrast those not typically explored in static architectures. The architecture models to be described allow for all of these features as each is a very important aspect of a programmable platform. As mentioned this table highlights the strengths of programmable platforms especially when dealing with concurrency and distributed control.

| Characteristic        | Description                                                                  |

|-----------------------|------------------------------------------------------------------------------|

| Spatial Computation   | Data processed by spatially distributing the computations                    |

| Configurable Datapath | Functionality and interconnection network of computational units is flexible |

| Distributed Control   | Units process data based on local control                                    |

| Distributed Resources | The required resources for computation are distributed throughout the device |

Table 1.2: Characteristics of Programmable Platforms

Table 1.3 shows the wide range of programmable devices. As the table progresses, the level of abstraction increases as does the intended scope of the device (from component to whole system). For this thesis, FPGAs, SoCs, and Hybrid Architectures will be focused on. This thesis is presented purposefully device agnostic. However, the key issue here is abstraction (the granularity at which the device is modeled). This thesis is going to look at functional and transaction level models. Therefore it is inappropriate to talk about PLDs. In addition, analog issues will not be explicitly mentioned therefore Field Programmable Analog Arrays (FPAAs) will not be covered.

| Device                                 | Description                                                    |  |

|----------------------------------------|----------------------------------------------------------------|--|

| Programmable Logic Device (PLD)        | PROMS, PLAs                                                    |  |

|                                        | Examples: Flash Memory Devices from Intel [Int04a]             |  |

| Field Programmable Gate Array (FPGA)   | Contains uncommitted configurable logic blocks (CLBs)          |  |

| *FOCUS of this thesis                  | Examples: Altera Cyclone FPGA [Alt04]                          |  |

| Field Programmable Analog Array (FPAA) | Contains uncommitted configurable analog blocks (CABs)         |  |

|                                        | Examples: Anadigm AN10E40 [Ana04]                              |  |

| System on a Chip (SOC)                 | Static and reconfigurable components at function unit level    |  |

| *FOCUS of this thesis                  | Examples: Cypress PSoC [Cyp04]                                 |  |

| Hybrid Architectures                   | Static and reconfigurable components at function and bit-level |  |

| *FOCUS of this thesis                  | Examples: Xilinx Virtex II Pro [Xil02]                         |  |

Table 1.3: Programmable Platform Technology Classification

Table 1.4 illustrates the various aspects which need to be considered when creating a model of a programmable architecture. The left column indicates the various aspects of programmable platforms that are of interest in a modeling framework. A description and example of each is provided in the right column. This thesis will be dealing with functional unit granularity and tight chip level host coupling. The other

factors do not directly apply to this thesis. Reconfiguration methodologies are not directly discussed (but can be modeled still) and arbitrary memory organizations can be modeled.

| Classification              | Description                                                                    |  |

|-----------------------------|--------------------------------------------------------------------------------|--|

| Granularity                 | Size of the smallest reconfigurable functional unit addressed by mapping tools |  |

|                             | Tradeoff between flexibility and performance overhead                          |  |

|                             | Examples: CLB, ADC, ISA (bit level, function unit, program control)            |  |

| Host Coupling               | Type of coupling to host processor                                             |  |

|                             | Loose System Level/Loose Chip Level/Tight Chip Level                           |  |

|                             | Examples: Through I/O (SPLASH);                                                |  |

|                             | Direct communication (PRISM); Same chip (GARP, Chameleon)                      |  |

| Reconfiguration Methodology | How the device is programmed                                                   |  |

|                             | Examples: bit stream (serial, parallel); dynamic; partial                      |  |

| Memory Organization         | How computations access memory                                                 |  |

|                             | Examples: large blocks vs. distributed                                         |  |

Table 1.4: Example Programmable Platform Architecture Classifications

Finally, Table 1.5 shows the potential design levels (abstractions) upon which programmable devices can operate. There are two axes. The left column is the vertical axis which represents abstraction. The other three right columns are the types of design element categories. This thesis will be concerned with both the *Microarchitecture level and the Process/Systems level*. System Level Design dictates that it only really makes sense to examine the levels above "Implementation". RTL based design would be more concerned with "Implementation level" and its goal would be to integrate the ESL solution with a tool that could traverse this portion of the design flow.

| Design Levels (Vertical Axis)      | Design Elements (Horizontal Axis) |                    |                       |

|------------------------------------|-----------------------------------|--------------------|-----------------------|

|                                    | Communication                     | Storage            | Processing            |

| Implementation                     | Switches/Muxes                    | RAM Organization   | CLB/IP Block          |

| Microarchitecture *FOCUS           | Crossbar/Bus                      | Register File Size | Execution Unit Type   |

|                                    |                                   | Cache Architecture | Interpreter Levels    |

| Instruction Set Architecture       | Address Size                      | Register Set       | Custom Instructions   |

| Process Architecture *FOCUS        | Interconnection Network           | Buffer Size        | Number/Types of tasks |

| <b>Systems Architecture *FOCUS</b> |                                   |                    |                       |

Table 1.5: Horizontal/Vertical Axis Classification Example [Pat01]

In summary, this thesis will be concerned with modeling architecture services for FPGAs, SoCs, and Hybrid Architectures at the functional unit granularity with details present regarding the microarchitecure and system level. Specific examples will be discussed regarding the Xilinx Virtex II Platform FPGA [Xil02] (hybrid architecture) in Chapter 2.

These sets of programmable platform categorizations were chosen since they are at the appropriate level of abstraction desired. Additionally, they are easily described as modular components. They are easy to characterize which will improve accuracy as well.

#### 1.4 Thesis Contribution

At this point the reader should now be familiar with the items necessary to understand the background, goals, and context of this thesis. This final section will attempt to make *very clear* the contribution of this research. Thus far this chapter has established several things:

- Introduced Heterogeneity, Complexity, and Time-to-Market pressures as the motivating factors in

this research. These factors must be addressed in order for EDA to move forward to new growth areas

and develop new methodologies for its continued success.

- Matched the design factors to the design solutions intended to resolve them (Heterogeneity to Modularity and Complexity to Abstraction).

- Identified the outcomes that are desired: **Accuracy and Efficiency** and the ability to meet Timeto-Market demands. It is not enough to simply create abstract and modular designs without being accurate and efficiency. It is clear that ESL adoption is dependent on the ability to ensure these qualities.

- Introduced METROPOLIS and METRO II as the ESL, FPM, platform-based design approaches that will be used to explore these concepts. In the event the one does not uses these frameworks, the required constructs have been outlined as well.

- Identified that Programmable Platform Architectures Services are going to be the focus of the architecture service modeling in the methodology to be described. Not only do these devices look to address the same concerns as ESL, but they also possess key characteristics which make architecture modeling at the system level more accurate and efficient. Creating one set of programmable components takes the place of creating a very large set of static components.

What now remains is to demonstrate how these contributions combine to create a design flow to accomplish the desired outcomes. What will be presented next are two approaches.

#### 1.4.1 Naïve Design Flow

Before presenting the approach to be elaborated on in this thesis, a naïve approach will be presented as an example of how design is often done and to clearly illustrate the advantages of the proposed approach.

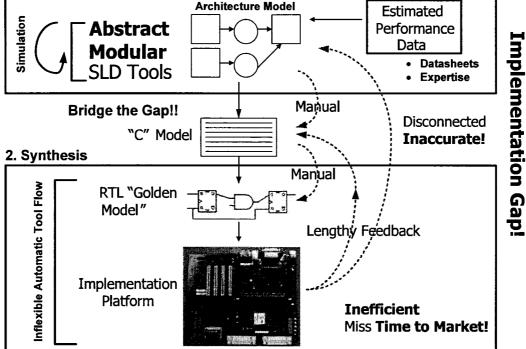

A typical simulation and synthesis design flow which minimally attempts to use ESL ideas (abstraction and modularity) may proceed something like this (Figure 1.12).

- Create an abstract and modular architecture service design in a system level design environment.

This will be accomplished in an environment supporting various models of computation and mapping strategies in the best case.